Cadence SPB Allegro and OrCAD 2022 (电子设计自动化软件) v22.10.005 Hotfix Only x64下载

Cadence SPB Allegro and OrCAD 2022 v22.10破解版是最好最专业的软件仿真和分析电子电路以及电子设计自动化软件部门(Electronic Design Automation或简称EDA)之一。OrCAD由两个词组成,实际上俄勒冈州是早期版本的发源地 软件和CAD代表计算机辅助设计,并形成了计算机设计手段。将Cadence SPB OrCAD或OrCAD PCB设置为Allegro PCB或其他已知方法,知识兔包括设计电路原理图,仿真和分析电路的各种程序。

Cadence SPB Allegro and OrCAD破解是两个流行的电路设计软件工具。它们都是Cadence Design Systems的产品,该公司是电子设计自动化(EDA)软件领域的领先分享商。

Cadence SPB Allegro破解版是一款全面的印刷电路板(PCB)设计工具,知识兔帮助工程师使用先进功能(如互连规划、约束管理和信号完整性分析)创建高性能设计。它支持从原理图捕获到板布局、制造和组装的整个PCB设计过程。

另一方面,OrCAD是一套用于电路仿真和PCB设计的软件工具。它包括原理图捕获、电路仿真、PCB布局和信号完整性分析工具。OrCAD被广泛应用于各种行业,知识兔包括航空航天、驾驶汽车、消费电子、医疗设备和电信,知识兔用于设计复杂的模拟和数字电路。

x64 | File Size: 3.32 GB

Description

OrCAD/Allegro one of the best and most professional software simulation and analysis electronic circuits and electronic design automation software division (Electronic Design Automation or abbreviated EDA) is.OrCAD consists of two words that in fact the state of Oregon was the birthplace of early versions of the software and CAD stands for Computer-aided design and computer design means is formed. Cadence SPB OrCAD OrCAD PCB set to Allegro PCB or also known, including various programs to design schematic, simulation and analysis of electronic is circuits.

Facilities and software features of Cadence SPB OrCAD

-suitable graphical user environments and display circuit using icons

-OrCAD Capture and Capture CIS schematic design circuits in powerful environment

-Ability to design PCB (Printed Circuit Board stands and means the board or PCB)

-has an extensive library full of components and electronic devices

-Advanced simulation and analysis electronic circuits in a graphical environment PSpice

-environment Orcad PCB Designer / Editor to design and edit PCB

-Ability to interact with MATLAB and Simulink software

System Requirements

OS:Windows 10 (64-bit) Professional, including Dark Theme mode; Windows Server 2012 (All Service Packs); Windows Server 2012 R2; Windows Server 2016.

CPU: Intel® Core™ i7 4.30 GHz or AMD Ryzen™ 7 4.30 GHz with at least 4 cores

Memory: 16 GB RAM

Space: 50 GB free disk space (SSD drive is recommended)

Display: 1920 x 1200 display resolution with true color (at least 32bit color)

GPU: A dedicated graphics card supporting OpenGL, minimum 2GB (with additional support for DX11 for 3D Canvas)

Monitors: Dual monitors (For physical design)

Supported MATLAB Version: R2019A-64Bit (For the PSpice-MATLAB interface)

Allegro和OrCAD都可以高度定制,并可根据个人用户的特定需求进行调整。它们还配有大量的元件库,使工程师能够快速创建和测试他们的设计。

- 合适的图形用户环境和使用图标的显示电路

- 在强大的环境中OrCAD Capture和Capture CIS原理图设计电路

- 设计PCB的能力(印刷电路板架和指电路板或PCB)

- 拥有一个广泛的图书馆,里面装满了元器件和电子设备

- 图形环境PSpice中的高级仿真和分析电子电路

- 环境的Orcad PCB设计器/编辑器来设计和编辑PCB

- 能够与MATLAB和Simulink软件进行交互

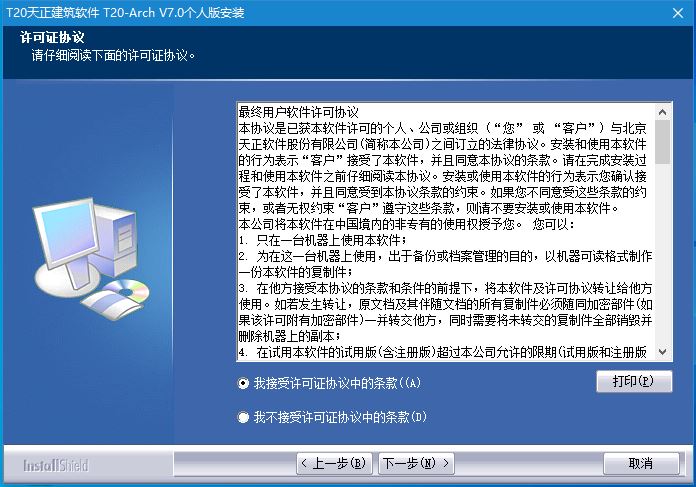

Cadence SPB Allegro and OrCAD 2022 v22.10破解版安装教程

一共有两个镜像文件:

- Cadence OrCAD and Allegro 22.1.iso

- Hotfix_SPB22.10.004.iso

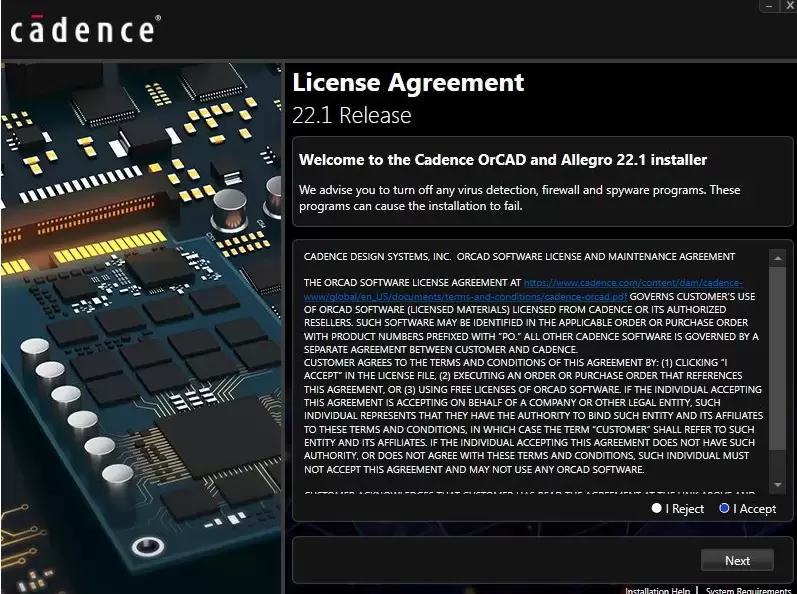

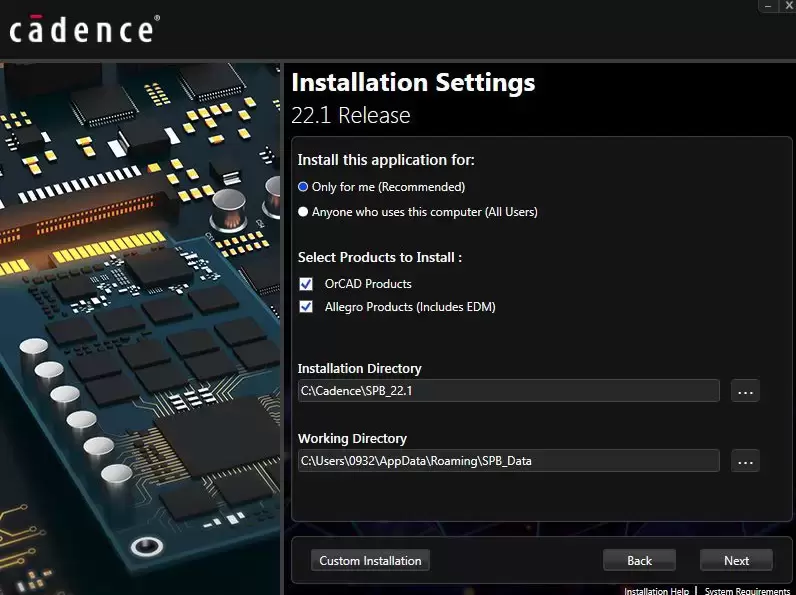

1,首先加载Cadence OrCAD and Allegro 22.1.iso镜像文件

知识兔双击Setup.exe选择安装目录安装软件

在Input License Details中,知识兔选择Connect to Existing License Server,知识兔点击Install安装即可

注:安装非常缓慢,一定要耐心等待安装完成

2,加载Hotfix_SPB22.10.004.iso镜像,知识兔双击Setup.exe安装升级补丁

3,全部安装完成后,知识兔打开Hotfix_SPB22.10.004.iso镜像中的MEDICINE文件

管理员身份运行CadenceLicensePatcher.exe,浏览选择Cadence的程序目录

比如我这里是D:\Cadence,知识兔点击Patch按钮打补丁即可(耐心等待,直到Patch OK)

4, 安装激活完成,Enjoy

22新功能

1、高速结构增强

高速结构已得到改进,知识兔以加快创作速度。现在,您还可以创建不包含焊盘入口或出口跟踪的结构,知识兔以维护当前路由和延迟匹配。还可以重新定义结构以覆盖现有结构或创建新结构。

2、差分对通孔被结构替换

注:此功能仅在带有高速选项的Allegro PCB Designer产品中可用。

在此版本中,更新了“用结构替换通孔”选项,知识兔以接受不包含焊盘入口或出口轨迹的结构,知识兔从而保持当前路由和延迟匹配。在版本17.4-2019,HotFix 028中分享了用结构快速更换差分对过孔的能力。尽管这种自动更换工作良好,但如果知识兔调整焊盘入口或出口轨迹以满足定时要求,更换可能会导致更换前不存在的延迟DRC。

3、论帆布结构的更新与变体的创造

结构可以在设计中多次使用。知识兔可以更新一个实例,并将更改推送到所有其他实例。有时,您可能需要添加或删除对象,或者为不同的应用程序创建稍微不同的结构变体。在此版本中,引入了“布线-结构-重定义”命令,知识兔用于在现有结构中添加或删除对象。然后知识兔,知识兔可以使用快捷方式命令覆盖实例或保存到新结构。

4、转换形状、过孔和销

注:此功能仅在Allegro PCB Designer、Allegro X Designer和Allegro Package Designer Plus产品中可用。

将GERBER或DFX文件转换为智能设计有时需要将这些文件转换为不同的设计对象以建立连接。例如,某些导入会导致需要“过孔”和“固定”对象的“形状”对象,或需要“连接线”对象的线对象。另一个设计活动是基于“曲线”、“线”和“固定或通孔垫”生成自定义形状,而不是手动跟踪对象。

此版本引入了几个实用程序,知识兔用于转换对象,并使用Tools–convert下的命令直接在画布上用焊盘堆栈创建或替换对象。

5、尺寸标注更新

使用“标注环境”命令可以在设计中的对象之间创建关联标注。因此,当移动或更改标注对象时,标注将自动更新。尽管维度的自动更新很有用,但切换到维度环境以删除或修改维度可能是一项繁琐的任务。此外,非关联标注被锁定,只能删除和重新生成。即使知识兔对维度进行微小的重新调整,也需要执行删除和重新生成维度的繁琐任务。

在本版本中,您可以将标注符号分隔为各个对象,知识兔以对标注进行更改,而无需删除和重新生成标注。要将标注拆分为单独的未关联对象,请选择“制造-标注环境”,然后知识兔选择“分解标注”命令。此命令既可以用于传统(非关联)标注,知识兔也可以用于关联标注。

6、路线禁止例外使用模型增强

尽管堆叠过孔在当今的设计中很常见,但在某些设计领域中不能使用。当然,您可以使用带有过孔列表检查的约束区域,但这可能会导致错误DRC错误的其他复杂性。

具有名为VIA_STACKING_NOT_ALLOWED的新形状属性的路线禁止形状的增强异常使用模型分享了一种简单的方法来检测堆叠过孔的位置并标记受限区域中的DRC。将此属性与VIAS_ALLOWED一起附加到路线禁止形状,知识兔以便可以在禁止形状内添加过孔,但如果知识兔存在堆叠过孔,则会显示DRC。

下载仅供下载体验和测试学习,不得商用和正当使用。