NI AWR Design Environment 22.1破解版下载

NI AWR Design Environment 22.1激活版(包括Microwave Office,Analog Office,Visual System Simulator,AXIEM和Analyst软件)推出了一种新的网络综合向导,知识兔用于多频段放大器和前端组件的阻抗匹配,高级设计编辑/选择,知识兔用于快速EM验证 进口RF /混合信号PCB,知识兔以及业界首个用于天线阵列设计的相控阵生成向导。此外,EM分析,设计流程自动化和可用性的进一步增强为客户分享了更高的生产力和设计成功

Cadence® AWR Design Environment® V22.1 软件包括以下新功能、增强功能和用户界面更改。这些变化对于 Cadence Microwave Office® 软件和 Cadence Visual System Simulator™ (VSS) 通信和雷达系统设计软件很常见。

AWR 设计环境平台支持版本控制软件的集成,知识兔以有效管理基于多种不同技术的复杂、多功能项目的组设计。您可以使用版本控制在多个设计师之间轻松协作并保留设计数据的修订历史记录。此版本的改进包括:

NI AWR Design Environment 22.1新功能特点

- 额外支持层处理文件 (LPF) 和自定义符号文件类型。

- 增强的文档导入错误处理,专门针对丢失或版本错误的 PDK。

- 能够使用“历史记录”对话框恢复到特定版本。

- 对基于文件的库和基于模块的库的设计同步集成支持。

- Cliosoft 集成修订现在显示修订 ID 而不是修订,并且知识兔状态现在是正确的。

- 对于添加到版本控制的项目,现在取消选中使用项目默认值选项,知识兔以确保项目之间的行为相同。

- 禁用的子电路现在包含在层次结构检查中。

- 现在按下 Escape 会关闭版本控制对话框。

- 全局定义文档现在在项目浏览器中移动时保留其版本控制状态。

- 如果知识兔将 EM 结构的 LPF 添加到源代码控制,存储库不再从版本控制对话框中消失

- 硅射频/毫米波 IP 创建,AWR 设计环境平台现在分享一个射频/微波设计创建环境,您现在可以使用 Microwave Office 软件中的 Virtuoso PDK 创建和分析硅射频/毫米波 IP,并与准备好分析、设计集成和后端验证流程的 Virtuoso 软件共享原理图和布局。。

- EMX 平面 3D 求解器集成:使用 Cadence EMX® Planar 3D Solver 从 AWR 平台内对硅 Virtuoso PDK 射频电路设计运行电磁分析。

- 与 Allegro 平台的互操作性增强:AWR 设计环境平台通过 Microwave Office 软件和 Cadence Allegro® PCB 设计工具之间的集成流程支持更广泛的 PCB 子系统设计流程。您现在可以在 Microwave Office 软件中创建和分析 RF/微波 IP,原理图和布局与 Allegro/DE-HDL 软件共享。

- 优化器增强:引入了一种新的指针 – 混合优化器方法,它结合了几个优化器的最佳性能,知识兔以在非常广泛的问题上产生最佳性能的算法。

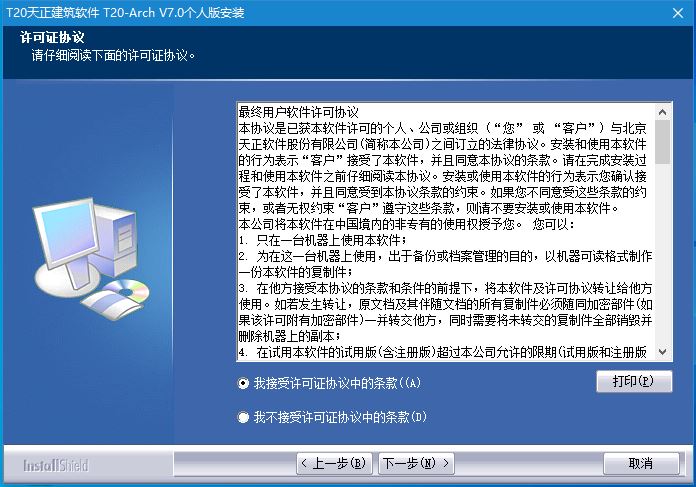

NI AWR Design Environment 22.1安装激活

1,知识兔双击Base_AWR17.00.000_wint_1of1.exe,知识兔选择软件安装目录,安装软件

2,软件安装完成后,知识兔打开Crack文件夹,复制所有文件到软件安装目录下

默认路径C:\Program Files (x86)\AWR\AWRDE\17

知识兔双击SolidSQUADLoaderEnabler.reg导入注册表

3,安装激活完成,Enjoy

下载仅供下载体验和测试学习,不得商用和正当使用。