Aldec ALINT-PRO 2021.09 x64免费版下载

ALINT-PRO™是用VHDL、Verilog和SystemVerilog编写的RTL代码的设计验证解决方案,专注于验证编码风格和命名约定、RTL和合成后仿真不匹配、平滑和最佳综合、正确的FSM描述、避免进一步设计阶段的问题、时钟和复位树问题、CDC、RDC、DFT,以及可移植性和重用编码。该解决方案基于 RTL 和 SDC™ 源文件执行静态分析,在设计周期的早期发现关键设计问题,从而大大缩短了设计签核时间。在RTL仿真和逻辑综合阶段之前运行ALINT-PRO可以防止设计问题蔓延到设计流程的下游阶段,并减少完成设计所需的迭代次数。

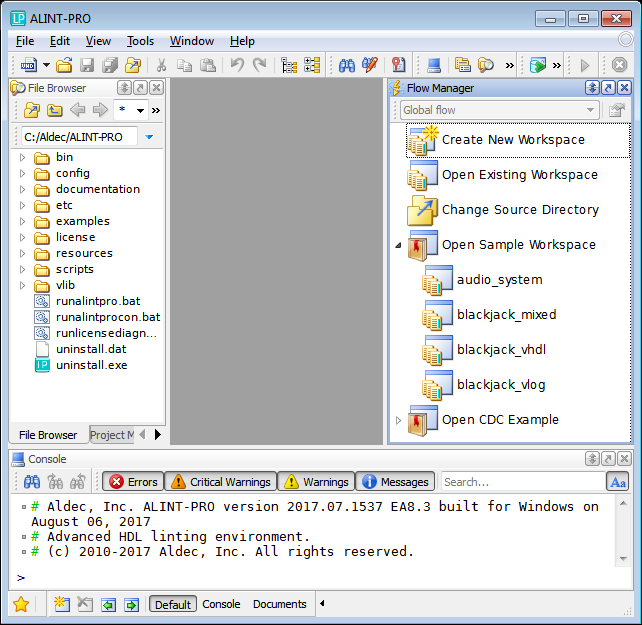

ALINT-PRO具有设计精良、直观的框架,提供高效的设计分析功能,包括RTL原理图查看器、FSM查看器、时钟和复位查看器、控制原理图查看器、详细说明查看器、违规查看器,以及用于时钟和复位域交叉分析的CDC查看器、RDC查看器和CDC原理图等特殊工具。

软件功能

1、静态设计验证

该软件是针对用VHDL、Verilog和SystemVerilog编写的RTL代码的设计验证解决方案,专注于验证编码风格和命名约定、RTL和综合后仿真不匹配、平滑和优化综合、正确的FSM描述、避免进一步设计阶段的问题、时钟和复位树问题、CDC、RDC、DFT以及可移植性和重用的编码。该解决方案基于RTL和SDC™源文件执行静态分析,在设计周期的早期发现关键设计问题,从而显着缩短设计签核时间。在RTL仿真和逻辑综合阶段之前运行该软件可防止设计问题蔓延到设计流程的下游阶段,并减少完成设计所需的迭代次数。

2、DRC和CDC/RDC分析的单一框架

知识兔软件具有精心设计的直观框架,它提供了用于高效设计分析的功能,包括RTL原理图查看器、FSM查看器、时钟和复位查看器、控制原理图查看器、详细说明查看器、违规查看器以及CDC查看器等特殊工具,用于时钟和复位域交叉分析的RDC查看器和CDC原理图。

通过读取外部项目文件格式(Aldec Active-HDL、Aldec Riviera-PRO、Xilinx Vivado、Xilinx ISE、英特尔Quartus)、解释典型仿真脚本(兼容命令,如vcom、vlog、vsim、vlib)以及用于批处理模式工具的传统文件列表,以及用于直接导入单个文件和整个目录的非常简单的GUI向导。

3、全芯片级Linting与单元Linting

知识兔支持2种不同的linting方法:全芯片级linting和单元linting。两种方法相辅相成,通常应用于设计周期的不同阶段。

完整的芯片级linting运行整个设计层次结构的分析,通用参数的特定值从顶层实例传播到叶子模块,并应用用户定义的时序约束。这种方法对于典型的HDL linting工具来说是传统的,并且更经常在签核期间使用,或者用于需要将整个设计作为一个已经集成的系统同时探索的验证类型(时钟和复位检查、CDC、RDC、DFT)。知识兔这种方法假设整个或至少大部分被测设计已经实现。

单元linting是一种相对较新的方法,可以很好地与平面处理相结合模式——一种特殊的细化,它认为HDL设计单元彼此独立,并且使用通用参数的默认值。这种处理风格高度容忍设计中缺失的元素,例如层次结构中尚未实现的部分。这使得单元linting在应用于单个源文件时最有价值,独立于其他文件,以及在设计人员修改文件之后。因此,许多非常有价值的规则检查很早就启用,甚至几乎在编写代码之后立即启用,从而将设计人员的反馈循环从几天或几周压缩到几秒钟。单元linting的一个自然应用是与HDL编辑器的集成,单元linting在后台运行,

单元linting并不能消除使用完整传统linting的需要,因为独立单元的组合可能会在集成后产生额外的问题。但是,系统地应用单元linting可以显着减少签核期间的验证量。

4、检查FPGA设计

该软件以最少的设置顺利地支持针对使用Xilinx、Altera、Microsemi和Lattice技术的FPGA实现的设计运行规则检查。提供最新版本的FPGA供应商库,这些库是预先构建的、默认安装的,并且预先配置用于高级时序和CDC规则检查。

知识兔软件为基于IP的FPGA设计自动设置分层和增量分析流程。每个IP块可以首先单独分析,提取的时序约束可以被提升和重新用于更快的更高级别的设计分析。除非在原始设计环境中重新配置IP块,否则它的主体只分析一次,从而在主FPGA设计的后续运行中节省大量时间。

5、批处理模式流

还可以通过一组丰富的基于TCL的脚本命令访问关键的功能。这些脚本可用于自动化设计规则检查、重复设置和报告生成。这些脚本可以在交互式控制台shell或全自动批处理模式下运行。最后,知识兔软件能够使用单个命令行shell应用程序调用以真正的批处理模式运行最典型的设计输入和linting场景,这使得它非常适合与更大的回归测试脚本和持续集成环境集成,例如詹金斯。

6、可用规则库

知识兔软件包括基于STARC(半导体技术学术研究中心)和RMM(重用方法手册)设计指南的规则库,它利用了世界各地半导体公司在设计开发中使用的最佳实践。对于安全关键设计,该软件提供基于DO-254指南的规则库,专注于影响设计稳定性的关键问题分析。对于RISC-V设计社区,该软件提供了RISC-V规则插件,该插件基于经过行业验证的最佳IP设计实践和指南。

主要规则插件辅以高度可配置的Aldec Basic和Premium规则库,这些规则库由该软件在FPGA和ASIC数字设计方面的内部经验驱动,并包括现有客户推荐的许多附加功能,以对抗芯片杀手工业规模设计中的问题。SV插件针对特定于SystemVerilog设计子集的新型RTL错误。

ALDEC_CDC规则插件将该软件转变为全面的CDC和RDC验证解决方案,能够在现代多时钟和多复位设计中进行复杂的时钟和复位域交叉分析和亚稳态问题的处理。知识兔软件中的验证策略由三个关键要素组成:静态结构验证、设计约束设置和动态功能验证。前两个步骤在该软件中执行,而动态检查通过与模拟器(Riviera-PRO™、Active-HDL™)的集成来实现,和ModelSim®支持)基于自动生成的测试平台。这种方法揭示了RTL模拟过程中潜在的亚稳态问题,否则将需要检测实验室测试。CDC和RDC问题的调试是通过丰富的原理图和HDE交叉探测机制以及综合报告和基于TCL的API实现的,允许浏览综合结果、时钟和复位结构、检测时钟和复位域交叉,并识别同步器。

下载仅供下载体验和测试学习,不得商用和正当使用。