SynaptiCAD(产品套件) v20.43下载

SynaptiCAD知识兔小编今天要为大家分享的SynaptiCAD是一款由电气工程师创建,旨在创建设计工具的电子设计自动化工具的集合包,它的功能强大,其中就包含了HDL输入,仿真,测试,波形分析,管脚映射工具等等,许多功能,是一个完整的电子设计自动化方案,其中最强大的九种工具就分别是TestBencher Pro 、 BugHunter Pro、 VeriLogger Pro、 WaveFormer Pro、SimuTAG、PinPort、DataSheet Pro、 Timing Diagrammer Pro、 Gigawave Viewer。因为知识兔这款软件是为那些工程师而制作的,所以软件以帮助工程师对其设计进行严格的思考为主。作为工程师本身,他们对必须几乎完成设计才能获得仿真结果感到沮丧。知识兔的创始人认为必须有一种更好的方法来与设计工具进行交互,并且知识兔从这个简单的想法开始,他们创建了SynaptiCAD,这是一家创建“思维专家工具”的公司。这个想法渗透到知识兔所有的工具界面中。软件以电气工程师为基础,知识兔以便制造草稿工具,这有助于工程师认真考虑其草稿。知识兔的工具会自动处理许多小细节,这些小细节会一直牵扯到草稿中,并让您有更多时间专注于较大的插图。

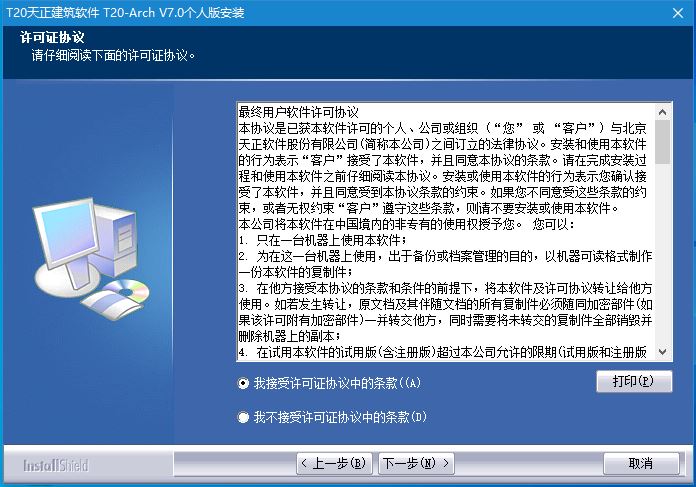

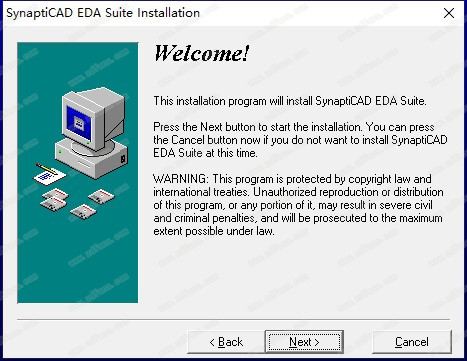

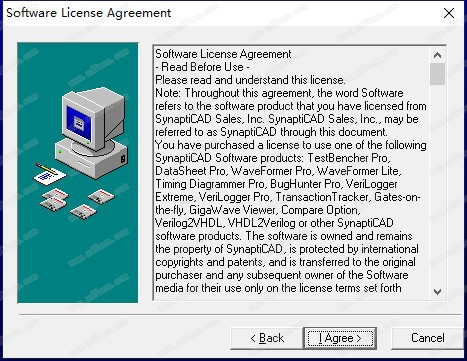

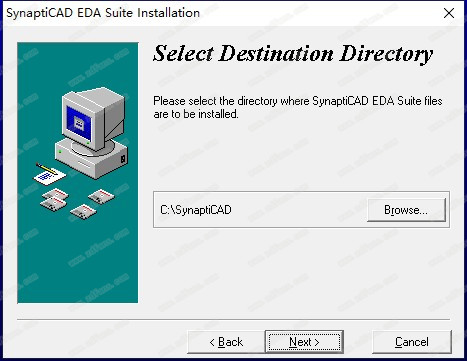

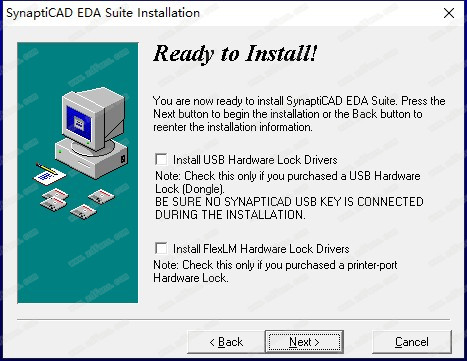

安装教程

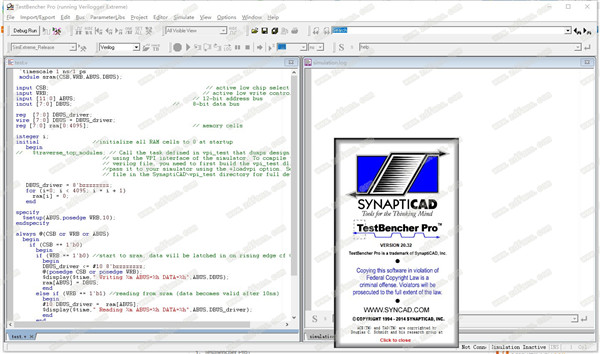

1、知识兔下载软件压缩包,知识兔点击“allproducts-20.32.exe”进行软件安装

2、阅读并同意软件安装协议

3、设置软件安装协议

4、确认安装信息,可选插件(自由安装),知识兔点击【Next】继续

5、由于软件工具较多,所以安装起来并不快,请耐心等待安装

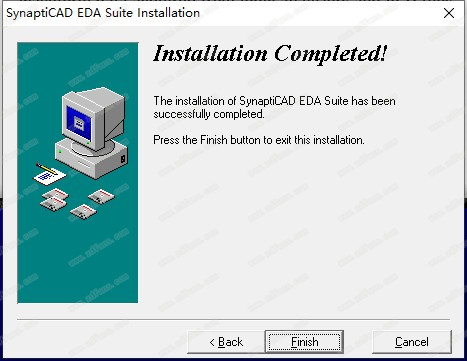

6、提示完成后,知识兔点击【Finish】按钮即可

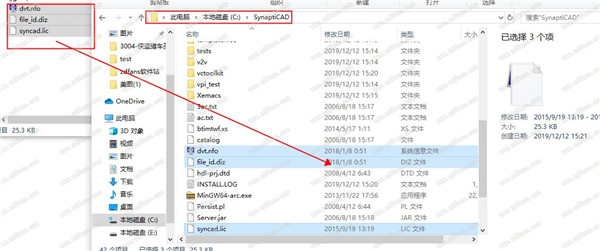

7、知识兔将破解补丁“syncad.lic”文件复制到根目录下默认路径为:C:\SynaptiCAD

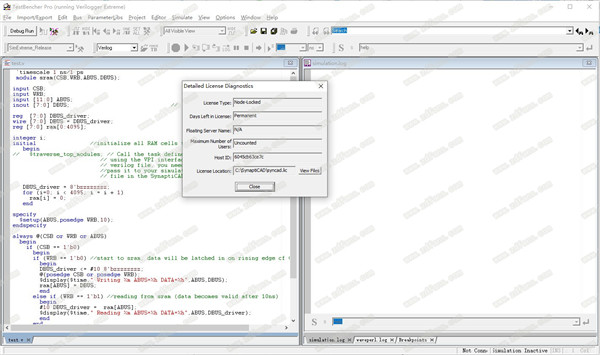

8、启动任意工具,在“帮助”菜单下打开注册框,知识兔选择注册文件“syncad.lic”

9、至此,SynaptiCAD全部安装完毕,请放心使用!

软件功能

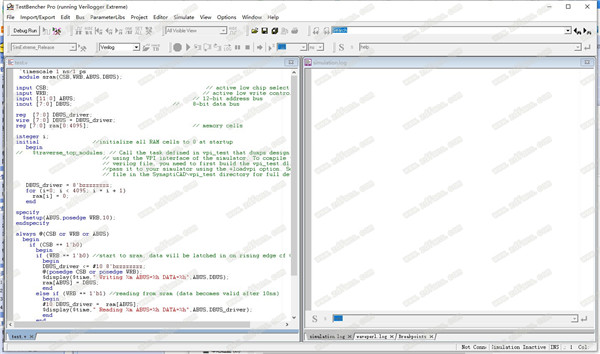

1.TestBencher Pro:用于从独立于语言的顺序逻辑表生成相互关联的VHDL,Verilog,OpenVera,e和TestBuilder测试基准及总线功能的模型。生成的测试基准能分享基于仿真的不同的激发矢量,,煞于测试基准功能作为一个被测试系统环境的动作模型正常工作。TestBencherPro是一个优秀的测试大规模FPGA和ASIC设计的工具。

2.BugHunter Pro:一种用于Verilog,VHDL和C ++模拟器的图形调试系统。BugHunter支持所有主要的HDL模拟器,其主要功能包括:单个步骤调试,波形数据串流,项目管理等等。知识兔可以侦测程序与帮助系统的交互过程从而发现问题所在。

3.VeriLogger Pro:Verilog模拟器软件。分享一个综合了传统的Verilog模拟器所有特征的仿真环境,它具有强大的图形测试矢量生成器。VeriLogger的快速模型测试使用户可以对设计中的每个模型进行“自底向上”的测试。

4.WaveFormer Pro:由时序图分析器,模拟器和测试矢量生成器组合放置。它为设计人员分享了一个集成的环境,知识兔可以使用开发数字和模拟线路的时序图。WaveFormerPro可以由Spice模拟器,Mathematica或Matlab等工具输入模拟数据。还可以利用WaveFormer Pro内部拥有的波形函数直接生成模拟信号;或者可以将总线上得到的数字信号转换成模拟信号。还可以将模拟信号波形逐段线性地变换成Spice模拟器的电压信号源。

5.SimuTAG:一种功能强大且实时地查证出FPGA的错误的系统。可通过比较FPGA功能规则反证RTL模式模拟规则,迅速发现逻辑和综合错误。

6.PinPort:分享数字硬件与Verilog或C ++的虚拟接口环境。

7.DataSheet Pro:时间表文件夹管理工具。

8.Timing Diagrammer Pro:日程设计工具。

9.Gigawave Viewer:波形观察器。

软件特色

1、项目级功能

Project Window中的New Port Mappings和Parm Mappings文件夹显示了测试模型如何连接到测试平台。此外,知识兔让用户更改映射。

Port Mappings图标颜色指示映射是默认映射(绿色)还是自定义映射(橙色)。在默认映射中,在测试平台中创建的信号与被测模型中端口的确切名称相匹配。当您想要测试诸如两个级联并行加法器电路之类的设计而不首先创建包装两个加法器的模块时,自定义映射会很有用。

2、BuHunter功能

tep Over和Step Into按钮将启动模拟器(如果知识兔尚未启动)。

GUI允许您在模拟完成后查询模拟状态,直到您按下红色“结束模拟”按钮。必须先按“结束模拟”按钮,然后知识兔才能开始新的模拟。

为GUI添加了模拟调用堆栈显示。这对于调试任务和函数的调用很有用。

3、时序图级别功能

在项目窗口中显示包变量以便于调试。

在“项目”菜单中添加了“导出时序图”,知识兔以将项目中列出的所有时序图导出为特定格式。此功能适用于WaveFormer Pro和DataSheet Pro。请参见第11.3节“导出一般说明”。

新的命令行选项-M将第二个时序图合并到正在加载的时序图(以前此功能只能从GUI访问,现在可以作为批处理操作执行)。

扩展VCD文件导入兼容性。

更新日志

1、SynaptiCAD的WaveFormer支持Agilent和Tektronix设备和Hyperlynx

2、时序图编辑器简化FPGA合成

3、VHDL / Verilog转换器升级为Verilog 2005

4、WaveFormer Lite为所有FPGA设计流程生成混合信号测试台

5、VeriLogger支持Actel,Altera和Xilinx

6、时序图的加密模型编辑分享可编辑的模拟方程式

7、SynaptiCAD的64位Verilog模拟器速度提高了30%>

下载仅供下载体验和测试学习,不得商用和正当使用。